Anhand der genauen Spezifikation wurde eine Entity mit allen Anschlüssen der Schaltung des Bausteins SN7496 programmiert, bei der die Ausgänge ausg als BUFFER charakterisiert sind, damit der Schiebefall simuliert werden kann.

In der folgenden ARCHITECTURE wurde ein Prozess schiebe für die einzelnen Arbeiten erstellt:

Clear:

Clockunabhängig

Setzt alle fünf Ausgänge auf Null

Serial Input:

Clockabhängig

Das angelegte Signal kommt auf den ersten Ausgang und wird dann entsprechend des Clock-Signales an die nächstfolgenden Ausgänge durchgeschaltet.

Preset Enable:

Clockunabhängig

Liegt hier 1 an, können die Preset-Eingänge dirket auf die Ausgänge gelegt werden.

Preset-Eingänge:

Somit ergibt sich folgender Quellcode der Schaltung SN7496:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY sn7496 IS

PORT (

ARCHITECTURE sn7496_innen OF sn7496 IS

BEGIN

schiebe:

PROCESS (preset, clk, pre_enable, ser_inp, clear)

BEGIN

END sn7496_innen;

Passend zur Schaltung wird eine Testbench programmiert, die einen Prozess ticker enthält, der die Clock simuliert.

Desweiteren enthält dieser Quellcode einen stimulus, der bestimmte Signale ausgibt.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY synth;

USE synth.vhdlsynth.all;

ENTITY testbench IS

PORT (

ARCHITECTURE tb_innen OF testbench IS

SIGNAL tempcyc: NATURAL := 0;

SIGNAL tempclk: std_logic := '0';

CONSTANT clk_period: TIME := 50 ns;

BEGIN

clk <= tempclk;

ticker:

PROCESS

BEGIN

stimulus:

PROCESS(tempclk, tempcyc)

--Hier Variablen deklarieren

BEGIN

END PROCESS stimulus;

END tb_innen;

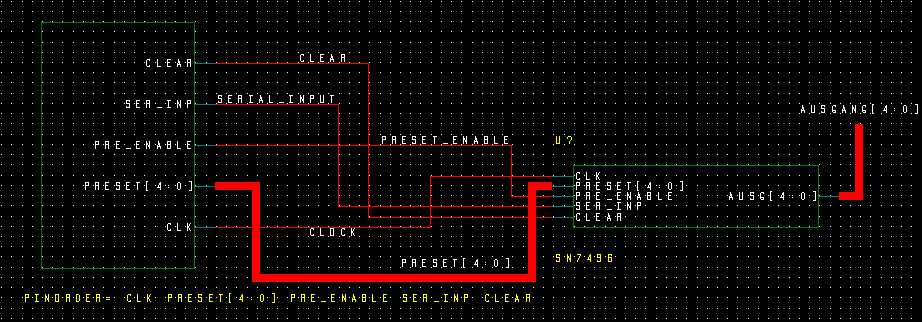

Um nun die Testbench mit der Schaltung zu verbinden, wird eine Top-Entity erstellt, die beide Schaltungen als Components enthält.

Sie enthält als Ports nur die Ausgänge des SN7496.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY synth;

USE synth.vhdlsynth.all;

ENTITY top IS

PORT (

ARCHITECTURE top_innen OF top IS

SIGNAL clk: std_logic;

SIGNAL preset: std_logic_vector (4 DOWNTO 0);

SIGNAL pre_enable: std_logic;

SIGNAL ser_inp: std_logic;

SIGNAL clear: std_logic;

-- name der schaltung

COMPONENT sn7496

PORT (

FOR BAUTEIL_eins: sn7496 USE ENTITY WORK.sn7496(sn7496_innen);

-- stimulus

COMPONENT testbench

PORT (

FOR BAUTEIL_zwei: testbench USE ENTITY WORK.testbench(tb_innen);

BEGIN

-- Bauteil_eins ist name.der.entity, Bauteil_zwei ist stimulus

BAUTEIL_eins: sn7496 PORT MAP (clk, preset, pre_enable, ser_inp, clear, ausg);

BAUTEIL_zwei: testbench PORT MAP (clk, preset, pre_enable, ser_inp, clear);

END top_innen;

Da der WaveView-Simulator leider eine nicht richtig arbeitende Beta-Version ist, konnte kein direktes Abbild der Waves hier eingebunden werden.

Allerdings konnte mit dem Hierarchy-Viewer die Richtigkeit der Schaltung überprüft werden.

Die hier abgebildeten Waves geben aber den Verlauf der Waves unserer Test-Entity und unserer Schaltung wieder.